本文來自格隆匯專欄:半導體行業觀察

半導體制程已經進展到了3nm,今年開始試產,明年就將實現量產,之後就將向2nm和1nm進發。相對於2nm,目前的1nm工藝技術完全處於研發探索階段,還沒有落地的技術和產能規劃,也正是因為如此,使得1nm技術具有更多的想象和拓展空間,全球的產學研各界都在進行着相關工藝和材料的研究。

上週,IBM和三星公佈了一種在芯片上垂直堆疊晶體管的新設計,被稱為垂直傳輸場效應晶體管 (Vertical Transport Field Effect Transistors,VTFET)。當前的處理器和SoC,晶體管平放在硅表面上,然後電流從一側流向另一側。相比之下,VTFET彼此垂直,電流垂直流動。該技術有望突破1nm製程工藝瓶頸。

IBM和三星表示,這種設計有兩個優點。首先,它可以繞過許多性能限制,將摩爾定律擴展到IBM當前的納米片技術之外,更重要的是,由於電流更大,該設計減少了能源浪費,他們估計VTFET將使處理器的速度比採用 FinFET 晶體管設計的芯片快兩倍或功耗降低 85%。IBM和三星聲稱,這一工藝技術有望允許手機一次充電使用整整一週。他們表示,它還可以使某些能源密集型任務(包括加密採礦)更加節能,因此對環境的影響較小。

IBM 和三星尚未透露他們計劃何時將該工藝技術商業化。他們並不是唯一一家試圖突破 1 nm瓶頸的公司。今年5月,台積電與合作伙伴發佈了1nm工藝技術路徑;7 月,英特爾表示,其目標是在 2024 年之前完成埃級芯片的設計。該公司計劃使用其新的“英特爾 20A”製程節點和 RibbonFET 晶體管來實現這一目標。

台積電依然是先鋒

近年來,科學界一直在尋找可以替代硅的二維材料,挑戰1nm以下的製程工藝,但至今未能解決二維材料的高阻、低電流問題。

近些年,在先進製程的研發和商業化方面,台積電一直是行業先鋒。

今年5月,台積電、中國台灣大學(NTU)和麻省理工學院(MIT)聯合宣佈,1nm芯片研發取得重大突破。

該突破主要體現在材料方面,使用半金屬鉍(Bi)作為二維(2D)材料的接觸電極,可以大大降低電阻並增加電流。這可以實現接近現有半導體尺寸物理限制的能源效率。該消息是在IBM早些時候宣佈其2nm芯片之後發佈的。

每一種新的工藝技術都會帶來新的挑戰,在這種情況下,關鍵挑戰是找到合適的晶體管結構和材料。同時,為晶體管供電的晶體管觸點對其性能至關重要。半導體工藝技術的進一步小型化增加了接觸電阻,從而限制了它們的性能。因此,芯片製造商需要找到一種電阻非常低、可以傳輸大電流並且可以用於量產的觸點材料。

使用半金屬鉍作為晶體管的接觸電極可以大大降低電阻並增加電流。目前,台積電使用鎢互連晶體管,而英特爾使用鈷互連。兩者都有其優點,並且都需要特定的設備和工具。

為了使用半金屬鉍作為晶體管的接觸電極,研究人員不得不使用氦離子束 (HIB) 光刻系統並設計一種“簡單的沉積工藝”。這種工藝僅用於研發生產線,因此還沒有完全準備好進行大規模生產。

目前,台積電的 1nm 製程節點仍處於探索階段,工廠正在嘗試各種選項,也不能保證未來量產時確定使用半金屬鉍。

IMEC指向2027

近日,比利時微電子研究中心 (IMEC)表示,1nm製程2027年就可實現商業化,之後的0.7nm 預計將在2029年後實現量產。

IMEC的CEO Luc Van den hove博士在接受採訪時強調,搭配全新技術,“摩爾定律要前進多少個世代都不是問題。”據悉,IMEC和ASML合作的EUV設備研發工作正在進行,日本的 TEL也參與其中,預計測試設備有望在2023年初完成,也有企業打算在2026年投入量產。

此外,IMEC還開發了一種新方法,可以在採用1nm製程工藝技術構建的芯片中使用金屬互連來減輕焦耳熱效應。

IMEC研究人員表示,在對基於鋁的二元化合物的實驗研究中,重點關注其電阻率,化學計量的AlCu和Al2Cu薄膜的電阻率低至9.5µΩcm。這些結果在實驗上支持它們在先進的半鑲嵌互連集成方案中用作新導體的承諾,在這些方案中,它們可以與氣隙結合以提高性能。然而,在這種組合中,焦耳熱效應變得越來越重要。這是通過在12層後端 (BEOL) 結構中結合實驗和建模工作預測的。

1nm製程需要在後端最關鍵的層中引入新的導體材料,如二元和三元金屬間化合物(例如,Al 或 Ru 基),其電阻率低於按比例尺寸的常規元素金屬(例如 Cu、Co、Mo 或 Ru)。IMEC已經通過實驗研究了鋁化物薄膜的電阻率,包括 AlNi、Al 3 Sc、AlCu 和 Al 2 Cu。在20nm 及以上厚度時,所有 PVD 沉積膜的電阻率與 Ru 或 Mo 相當或更低。28nm 的 AlCu 和 Al 2膜的最低電阻率達到 9.5 µΩcmCu – 低於 Cu 的值。

IMEC設想在先進的半鑲嵌集成方案中引入金屬間化合物,包括直接蝕刻可圖案化金屬以實現更高縱橫比的線條。通過在金屬線之間逐漸引入部分或全部氣隙,可以進一步改善 RC 延遲。用電隔離氣隙代替傳統的低 k 電介質有望降低按比例尺寸的電容。但是氣隙的導熱性極差,這引起了對操作條件下焦耳熱的擔憂。

IMEC通過在局部 2 層金屬互連級別執行焦耳熱“校準”測量並通過建模將結果投影到 12 層 BEOL 結構,量化了這一挑戰。該研究預測,空氣間隙會使温度升高 20%。發現金屬線的密度起着重要作用:較高的金屬密度顯示有助於降低焦耳熱。

“這些研究結果是改進半鑲嵌金屬化方案作為1nm製程互連選項的關鍵,” IMEC研究員兼納米互連項目總監 Zsolt Tokei 説。“此外,IMEC正在通過其它選項擴展互連路線圖,包括混合金屬化和新的中間線方案,同時解決與工藝集成和可靠性相關的關鍵挑戰。”

1nm之後將如何發展?

當硅基芯片突破1nm之後,量子隧穿效應大增,將形成“電子失控”,使芯片失效。這種情況下,替換芯片的硅襯底,也許是芯片進一步發展的可行出路之一。

電子可以連續地從一個門流向下一個門,而不是停留在預期的邏輯門內,這在本質上使得晶體管不可能處於關閉狀態。

由於晶體管由三個端子組成:源極,漏極和柵極。電流從源極流向漏極,並由柵極控制,柵極根據施加的電壓而進行導通或關斷電流。

硅和二硫化鉬(MoS2)都具有晶格結構,但是通過硅的電子有效質量比二硫化鉬小。當柵極長度為5nm或更長時,硅晶體管可以正常工作。

而通過二硫化鉬的電子有更高的有效質量,他們的流動可以通過更小的門長度來控制。勞倫斯伯克利國家實驗室對此方案的可行性進行了實驗驗證,但該研究仍處於非常早期的階段。

一個14nm製程芯片上有超過10億個晶體管,而伯克利實驗室團隊還沒有開發出一種可行的方法來批量生產新的1nm晶體管,甚至還沒有開發出使用這種晶體管的芯片。

但是哪怕僅僅作為概念的證明,這裏的結果仍然是非常重要且令人鼓舞的,期待後續新材料的發現可以繼續允許更小的晶體管尺寸,並隨之提高未來芯片的能效。

中國也有亮點

目前,全球1nm製程工藝都處於研發探索階段,距離商業化生產還要幾年的時間。因此,雖然中國大陸地區的先進製程工藝的商業化水平不高,但在相關的理論研究方面也在跟隨國際前沿。例如,湖南大學在1nm製程工藝的研究方面也有亮眼的表現。

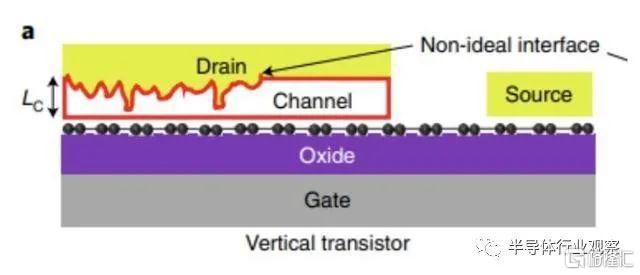

今年6月,湖南大學的研究團隊研發出了超短溝道的垂直場效應晶體管(VFET)。這種晶體管技術,可以把晶體管做到3nm大小,而溝道長度只需要0.65nm。在以往的製程工藝中,溝道長度代表的就是芯片製程,也就是説0.65nm的溝道長度,就意味着0.65nm製程。

就是晶體管不是平行排列的,是垂直排列的。這種縱向的結構具有天然的短溝道特性,半導體溝道位於底電極與頂部電極之間,溝道長度僅取決於材料厚度。

更重要的是,這種垂直場效應晶體管不是平行排列的,是垂直排列的。這種縱向的結構具有天然的短溝道特性,半導體溝道位於底電極與頂部電極之間,溝道長度僅取決於材料厚度。

研究人員採用了範德華(vdW)金屬電極集成方法,以二硫化鉬(MoS2)作為半導體溝道的薄層甚至單原子層,也就是説溝道長度,其實就是一層二硫化鉬材料的厚度,所以最短達到了0.65nm。由於排列方式的不同,無需縮短晶體管與晶體管之間的距離,搭積木式的一層一層往上壘就行了,這就使其不完全依賴於高精度光刻機。不過,該研究只是實驗室的產物,要真正走向量產,還有很長的路要走。

向1nm光刻機進發

以上談的都是工藝技術和材料的研發,要實現1nm製程的落地,製造設備,特別是EUV光刻機是必不可少的,這就不得不提到ASML。

目前,ASML的主力出貨EUV光刻機分別是NXE:3400B 和3400C,這兩款機型的數值孔徑(NA)均為0.33,其中更新一款的3400C 的可用性已經達到90% 左右。

ASML預期,到今年年底,NXE:3600D 將會開始進行交付,該設備的匹配套精準度提升了,在30mJ/cm2下的晶圓吞吐量達到160片,相比3400C提高了18%,將會成為未來台積電和三星3nm製程工藝的主要設備。

除此之外,ASML還公佈了未來的三代光刻機研發計劃,三款機型的型號分別是NEXT、EXE:5000 和EXE:5200。從EXE:5000開始,將數值孔徑提高到了0.55。

0.55NA 比0.33NA 有着巨大的提升,包括更高的對比度,圖像曝光成本更低等,是未來發展的趨勢。

目前,硅片、曝光潔淨室已經逼近物理極限,現在的5nm/7nm 光刻機變得十分精密,設備零件多達10萬+、體積為40個貨櫃。據悉,1nm 光刻機體積要比現在3nm 的多出一倍。

由於光刻機擁有非常多的零件,需要高精度的裝配,導致光刻機從發貨到配置/培訓的整個流程需要長達兩年時間。按照這個參考推算,預計0.55NA 的大規模應用得2025~2026年了,那時,大概率是1nm製程工藝試產時段。

結語

以上這些只是目前行業內進行1nm製程相關研發工作的代表,並非全部。相信隨着3nm的量產,以及2nm進入商業化階段,1nm製程的研發會逐步成熟,當下的這些實驗室級研究,預估將有不少會落地到晶圓廠,同時,還將會有更新的工藝和材料技術誕生。