本文來自格隆匯專欄:半導體行業觀察

多層排線技術支撐3納米

在之前的文章中,我們探索了“更先進的晶體管技術(Post Silicon)”,具體而言,通過將作為2D材料的過渡金屬二硫屬化物(TMD,Transition Metal Dichalcogenide)用於溝道(Channel),以實現1納米以下技術節點的目標。

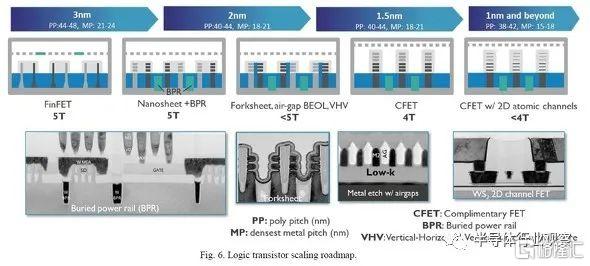

本文開始介紹第五項“新一代多層排線技術(BEOL)”。負責3納米以後技術節點的多層排線技術(BEOL)是本文的主題。首先,我們看下微縮化技術藍圖。

3納米以後的CMOS邏輯電路的技術藍圖

排線微縮化技術藍圖。此圖是筆者根據上面圖紙中排線的相關數值彙總的

三年來,金屬排線的最小Pitch(MP)的技術發展藍圖如下:5納米技術節點為28納米、3納米技術節點為21納米、2納米技術節點為16納米。此外。CGP的發展藍圖如下:5納米技術節點為48納米、3納米技術節點為45納米、2納米技術節點為42納米。

而從最新的技術藍圖中可以看出來,金屬排線的微縮化發展越來越慢。3納米節點的MP為21納米一一24納米、CGP(或者PP)為44納米一一48納米。2納米節點和1.5納米節點的MP為18納米一一21納米,CGP為40納米一一44納米,1.0納米以下節點的MP為15納米一一18納米,CGP為38納米一一42納米。在以往的技術藍圖中,金屬排線的Pitch(MP)微縮化是從21納米直接過渡到16納米。而在最新的技術藍圖中,21納米的後面為18納米、15納米,發展較緩。

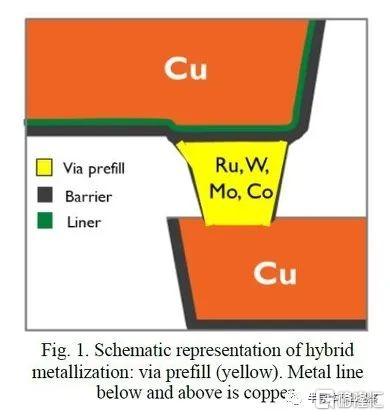

支持着最新的CMOS邏輯電路的多層排線技術採用的是銅(Cu)質排線。而製造工藝採用的是Damascene技術(一種通過蝕刻絕緣膜,在溝槽中鍍金屬的技術,俗稱“大馬士革技術”或“鑲嵌技術”)和CMP技術(一種平坦化技術)。

銅(Cu)質排線的缺點是隨着微縮化的發展,排線的電阻會急劇增加。由於銅原子易於擴散於周邊,因此將Barrier層(防止銅原子擴散)置於銅金屬層與絕緣膜之間。而Barrier層電阻高、很難做到更薄。因此,如果縮小銅排線層斷面厚度,Barrier層(高電阻層)的厚度就會增加。

要緩解因微縮化而帶來的電阻增大問題,有兩個辦法。其一,加厚銅排線層。其二,將排線金屬改為不需要Barrier層的材料。在imec演講中,主要敍述了“嘗試將排線金屬由銅(Cu)改為釕(Ruthenium)”。

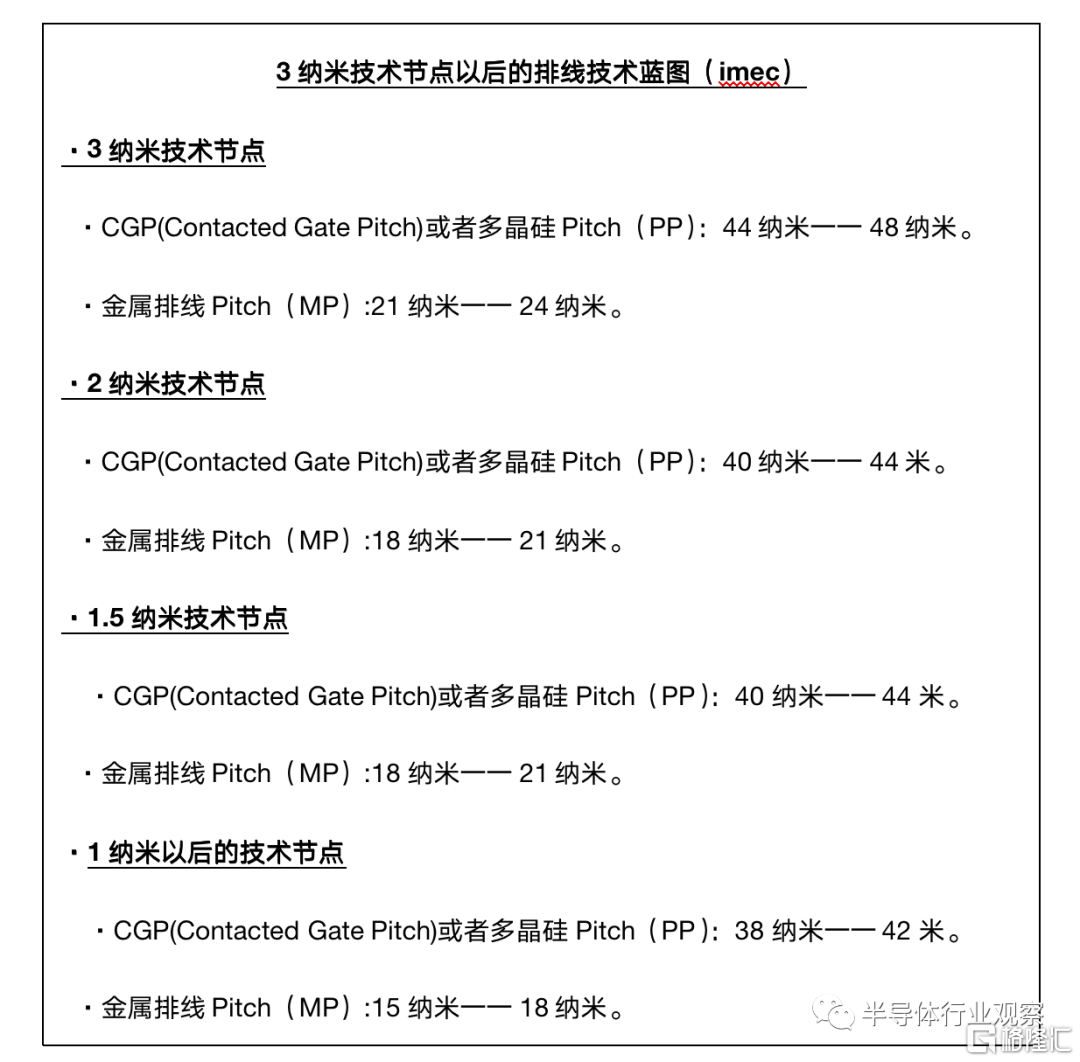

即使在現行的Lithography (微影)技術中,也做到與16納米(2納米技術節點)Pitch平行的平行線路。將ArF浸液光刻技術與Multi-patterning技術(多重圖形技術)融合。Multi-patterning技術選用的是SAOP(Self Aligned Octuple Patterning,自對準型八重曝光)。依據以上這些技術,imec於2018年公佈稱,已經成功試做與16納米Pitch平行的排線線路。

電子顯微鏡下觀察,與16納米Pitch平行的排線線路斷面圖

新的多層排線技術有助於實現2納米

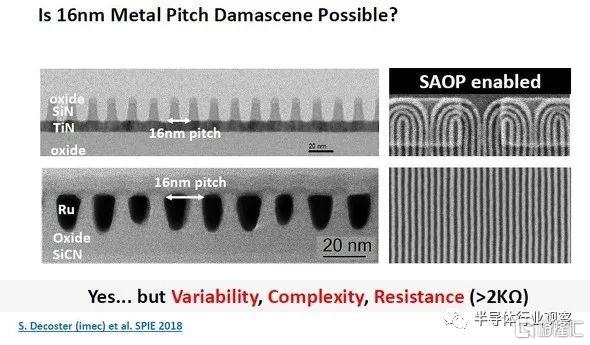

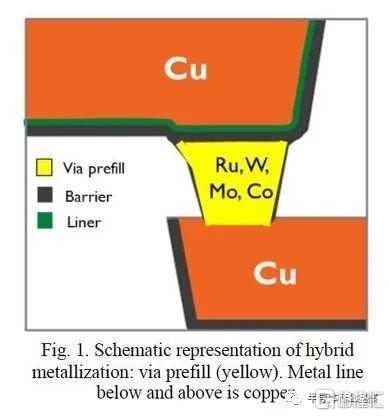

多層排線的導體部分由平行的直線排線羣層(排線層)和連接各層的導孔(Via)電極構成。最先迎來微縮化極限的是導孔電極。於是,導孔電極的材料不再採用銅,而是改為鎢(W,Tungsten)、鉬(Mo,Molybdenum)、鈷(Co,Cobalt)、釕(Ru,Ruthenium)等熔點較高的金屬。

多層排線斷面圖:排線層為銅、導孔電極為熔點較高的金屬

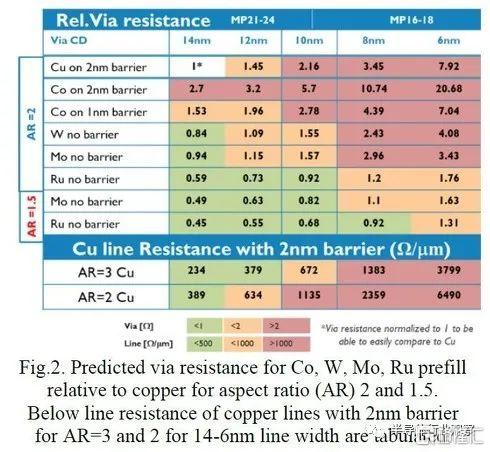

因導孔電極微縮化而引起的銅和高熔點金屬電阻值的變化(比較銅和其他高熔點金屬,上圖中的數值為計算值)。用銅填埋縱橫比(Aspect Ratio,AR,Barrier層厚度為2納米)為2的導孔(最小尺寸CD為14納米)時的電阻值定為單位“1”後,得出以上數值。

用厚度為2納米的Barrier層和銅來填埋最小尺寸(Critical Dimension,CD)為14納米的導孔(相當於排線Pitch為21納米一一24納米的多層排線結構)後,把導孔的電阻值(導孔的縱橫比AR為“2”)定為單位“1”。如果導孔寬度微縮至10納米,電阻值(相對值)會超過單位“1”的兩倍以上,為2.16。

另一方面,同樣導孔(AR為2)最小尺寸為14納米,且無Barrier層的鎢電阻值(相對值)為0.84,鉬為0.94,釕為0.59,電阻值都低於銅。

此外,當排線寬度為14納米、縱橫比(AR)為3時,銅質排線的電阻值(此處為:每單位長度的電阻值)為234Ω/μm,AR為2時,銅電阻值為389Ω/μm。如果排線寬度微縮至10納米,當AR為3時,電阻值為672Ω/μm,當AR為2時,銅電阻值為1135Ω/μm,電阻值增加到2.9倍。

基於以上推測,imec認為未來釕(Ru,Ruthenium)有望成為多層排線材料。其理由如下:電阻率低、不需要Barrier層、可進行蝕刻加工等。

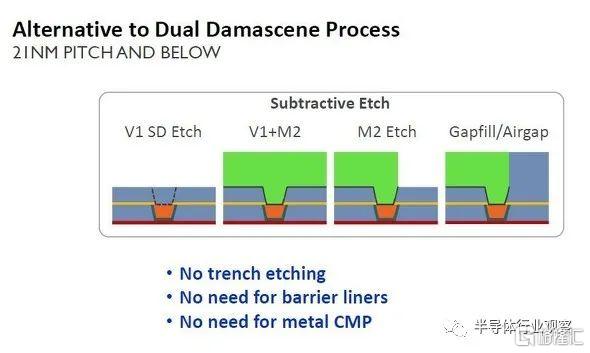

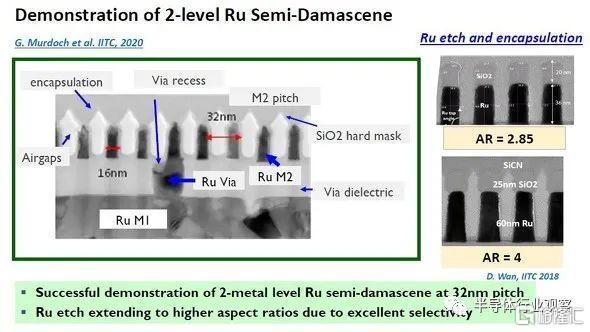

於是,imec正在利用一種被稱為“半鑲嵌(Semi Damascene)”的技術,來研發釕材質的多層排線結構。在“半鑲嵌”技術中,首先在下層的排線層上形成絕緣膜,並蝕刻形成導孔。其次,同時在上層的排線層(Ru層)和導孔上形成絕緣膜。最後,蝕刻導孔周圍後,用絕緣膜填埋、或者留下“空氣間隙(Air Gap)”。

“半鑲嵌(Semi Damascene)”技術工藝。利用成膜和蝕刻,形成排線和導孔電極。導孔的周圍為絕緣膜或者空氣間隙

從銅排線改為釕後的技術藍圖

Imec正在利用一種名為“半鑲嵌(Semi Damascene)”的技術研發釕(Ru,Ruthenium)多層排線結構。就“半鑲嵌(Semi Damascene)”的技術而言,它是在下層排線層的上面形成絕緣膜、蝕刻導孔。然後,在上層的排線層(Ru層)和導孔上形成絕緣膜。最後,蝕刻導孔周邊後,用絕緣膜填埋、或者留下“空氣間隙(Air Gap)”。

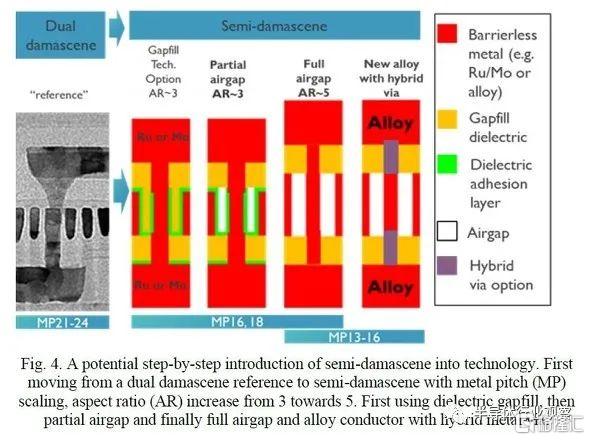

從銅排線改為釕(Ru,Ruthenium)排線後的微縮化技術藍圖在“IEDM 2020”的演講(論文編號 32.2)中已經公佈。21納米一一24納米Pitch是採用“雙鑲嵌結構(Dual Damascene )”技術形成銅排線或者釕排線。釕排線和“半鑲嵌技術”都是始於16納米一一18納米Pitch。相鄰的排線之間和上下排線層之間由介電常數較低的的絕緣體填充。排線的縱橫比(AR比:縱/橫之比)為2.5左右。3也是被選項之一。

即使是16納米一一18納米Pitch,在進入下一代際後,也會將排線的縱橫比(AR比)提高至3,降低電阻值。通過在相鄰排線間的絕緣層中留出一部分“空氣間隙(Air Gap)”,來控制靜電電容值的增加。

在新的代際(16納米一一18納米Pitch之後的13納米一一16納米Pitch)中,會把排線的AR比提高至5,以進一步降低電阻值。相鄰排線間的絕緣層全部由“空氣間隙(Air Gap)”完成,以控制靜電電容值的增加。

要實現13納米一一16納米Pitch,採用釕金屬會存在不少困難。因此很有可能會採用其他金屬或者合金用於排線、導孔電極。

從銅排線向釕排(Ru)線的過渡,釕排線微縮化發展藍圖

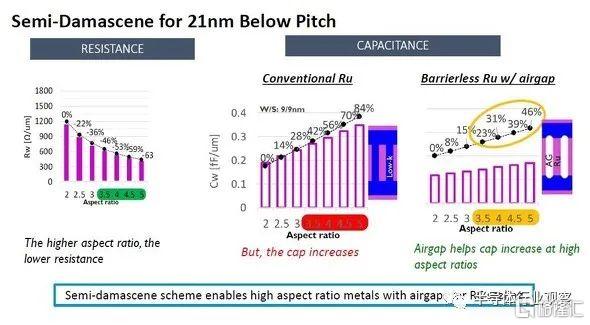

下面我們説明一下導入微縮化技術藍圖的技術要素。排線微縮化的主要弊端在於電阻值的增加和較低的抗電遷移(Electromigration)性。但是二者都可以通過提高排線的AR比得以緩解。比方説,將AR比從2提高至3.5的話,單位長度的電阻值可以下降50%左右。

但是,如果提高AR比,就會出現排線間靜電電容值增加的問題。比方説,如果將AR比從2提高至3.5,單位長度的電容值會增加42%。

要解決這一問題,可以在相鄰排線間的絕緣部分導入“空氣間隙(Air Gap)”。“空氣間隙(Air Gap)”的相對介電常數(Relative Permittivity)為“1”,理論上是介電常數最低的絕緣物體。一旦導入“空氣間隙(Air Gap)”,就可以將AR比為3時的靜電電容值控制在23%。

釕(Ru)排線的AR比和電阻值以及靜電電容值的關係。電阻值和靜電電容值都基於單位長度的

Imec已經成功用釕(Ru)試做了32納米Pitch(採用“半鑲嵌”技術和空氣間隙技術等)的兩層排線。第一層金屬排線、導孔電極、第二層金屬排線全部採用釕材質。

電子顯微鏡下觀察,第一層金屬排線、導孔電極、第二層金屬排線全部採用釕材質的雙層排線結構的斷面圖,排線Pitch為32納米

導孔電極的微縮化支撐高密度化

接下來,我們談談多層排線技術的核心一一導孔電極技術。

導孔電極指的是連接上下排線層的圓柱狀的電極。由在排線層間的絕緣膜中形成的細長孔和埋於孔中的金屬構成。通常,與排線層的厚度相比,導孔電極的直徑較短。如果收窄排線的寬幅,導孔電極就會增加、抗電遷移(Electromigration)性也會下降。如果將銅質多層排線微縮化,銅導孔電極的電阻會明顯增加,同時,電遷移(Electromigration)的壽命會變短。於是,考慮僅把導孔電極的金屬改為熔點較高的金屬。這在上文已經説明。

多層排線層的斷面圖,其中排線層為銅、導孔電極(黃色部分)為熔點較高的金屬

最尖端的CMOS的多層排線多采用以下佈局(Layout),各層平行的直線羣通過上下相連的層來直接相連。比方説,從最下層(第一層或者稱之為“M1”)開始數,奇數層的排線為水平方向(橫向)延伸,偶數層(第二層或者稱之為“M2”),的排線為垂直方向(縱向)延伸。由於一般的導孔電極是連接上下相連的排線層的,因此此處的導孔電極為連接水平排線和垂直排線的交叉點。

但是,最近,人們開始認為連接鄰近奇數層(或者偶數層)的導孔電極也很重要。比方説,用導孔電極連接M1和M3。這種導孔電極的作用是可以有效降低下層排線的電阻值,提高抗電遷移(Electromigration)性。

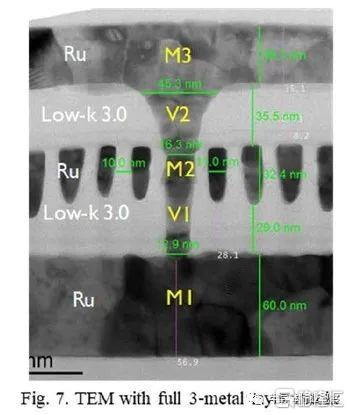

電子顯微鏡下觀察,釕(Ru)材質的三層排線層的斷面(試作品)。M2(第二層)為橫切、M1(第一層)、M3(第三層)為平行方向。M1何M3的排線Pitch為36納米、M2為21納米,導孔(Via)的直徑(V1,連接M1和M2的導孔)為12.9納米,V2(連接M2和M3的導孔)為16.3納米一一45.3納米

通常,三層排線的最上層和最下層由2個導孔電極和1層排線層連接。為了方便,我們將連接M1和M2的導孔成為“V1”,稱連接M2和M3的導孔為“V2”。要連接平行的M1和M3,需要經由2個導孔和1個排線層。即,V1、M2、V2。M2是用於連接V1和V2的,因此不是具有細長的排線,因此多采用柱狀。我們這種結構為“疊加導通孔(Stacked Via)”。

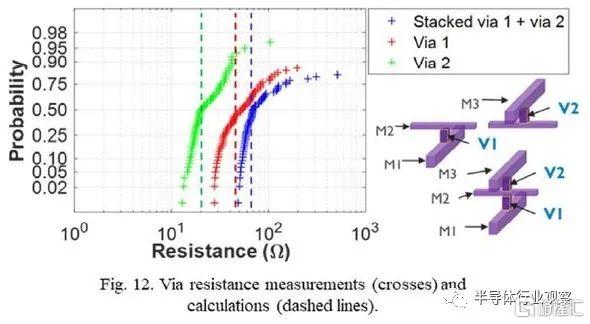

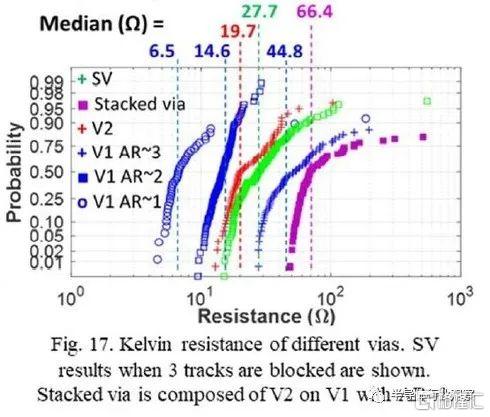

導孔電極的電阻值(累積概率)。此處為導孔電極的試作品的測量值

就imec試做的釕材質的三層排線而言,中間的M2的Pitch最狹窄,因此,V1的電阻稍高,V2的電阻稍低。此外,V1、M2、V2“疊加導通孔(Stacked Via)”電阻最高。

降低疊加導通孔(Stacked Via)電阻的方法之一是將M2層做得厚一些,但是,如果M2做得過厚,就會影響周邊的M2的配置,影響整體的佈局。此外,直接連接M1和M3(不經過M2)的“Super Via(超級導孔)”也在被人們考慮,將在下文中敍述。

“Super Via” 可有效降低多層排線的電阻

接下來我們就“Super Via(超級導孔)” 技術展開敍述,這是一種可以降低直接連接奇數層(或者偶數層)的導孔電極的電阻的技術。

現在已經開始採用一種名為“疊加導通孔(Stacked Via)”的技術,即一種以垂直方向連接奇數層(或者偶數層)的導孔電極。下面我們設想一下連接第一層金屬排線(M1)和第三層金屬排線(M3)的導孔電極。利用“疊加導通孔(Stacked Via)”技術,首先製造出連接M1和第二層金屬排線(M2)的導孔(V1),然後製作M2。其次,再製造連接M2和M3的導孔,最後成膜製成M3。

疊加導通孔(Stacked Via)技術的缺點如下,與連接M1和M2(或者M2和M3)的導通孔電阻相比,連接M1和M3的電阻值的電阻值會變得較高,且導孔的生產工藝會很複雜。

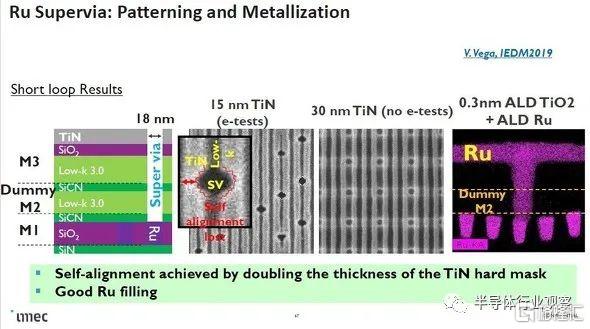

於是,開始考慮一種可以直接連接M3到M1的“Super Via(超級導孔)”。製作工藝如下:首先製作M1和M2(或者Dummy M2,即虛設的M2),然後在M2上形成絕緣膜。其次,堆疊氮化鈦(TiN, Titanium Nitride)硬膜(Hard Mask),然後開鑿一個可以貫通到M1表面的垂直孔(即,Super Via)。最後,將高熔點金屬(比方説釕)埋入到超級導孔(Super Via)內,同時,形成M3。

連接第三層金屬排線層(M3)和第一層金屬排線層(M1)的超級導孔工藝。左邊為結構圖,M2為虛設層(Dummy)。右邊圖像為在X射線掃描電鏡能譜儀(EDS設備)和電子顯微鏡下觀察的形成M3後的斷面圖。中間的兩張圖像如下,各種厚度TiN層所對應的導孔的類型。如果將TiN層做到30納米,就可以獲得良好的導孔

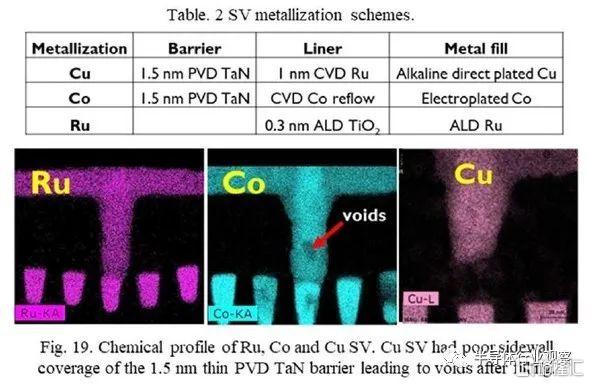

Imec分別試做了銅(Cu)、鈷(Co)、釕(Ru)材質的可以連接M1和M3的超級導孔,結果如下:銅無法充分地填埋導孔底部內壁,鈷會使導孔電極內部發生Void(空孔)。能形成良好的導孔電極和M3的只有釕。

上圖是試做的銅(Cu)、鈷(Co)、釕(Ru)材質的可以連接M1和M3的超級導孔。上面的表格是Barrier層、Liner、排線金屬、成膜方法。下面的圖片為在EDS設備和電子顯微鏡下觀察的斷面圖像

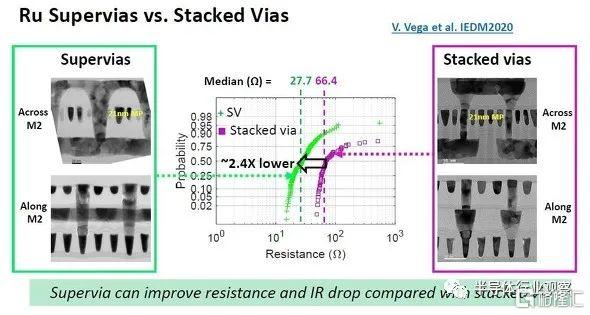

後來,又試做了釕材質多層排線,並比較了採用之前的技術疊加導通孔和超級導通孔情況下,連接M1和M3的導孔的電阻值。M1和M3為互相平行的直線羣、排線Pitch為36納米;M2為與M1(以及M3)成九十度的平行直線羣,排線Pitch為21納米。

利用傳統技術試做的導孔電阻值(中間值)為66.4歐、超級導孔為27.7歐。超級導孔的電阻值較傳統技術減少了1/2.4(42%),得以大幅度減少。

超級導孔(左邊)、傳統技術(Stacked Via,右邊)下的電阻值(測定值)。圖像為電子顯微鏡下觀察的斷面圖。排線Pitch如下,M2為21納米,M1和M3為36納米

“Super Via”所面臨的問題

Imec所推測的超級導孔有效發揮作用的排線結構如下:連接第一層金屬排線(M1)和第三層金屬排線(M3)。理論上的標準單元如下:垂直方向(縱向)上為平行的直線狀的M1和M3,水平方向(橫向)上為平行的直線狀的第二層金屬排線層(M2)。在此標準單元下,如果想要直接連接M1和M3,M2肯定是一個“障礙物”。換句話説,是超級導孔技術“阻礙(Block)”了M2。

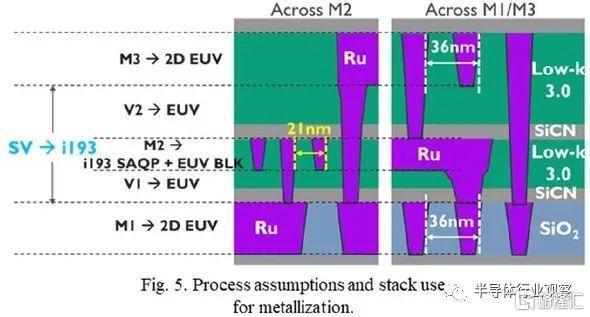

3納米代際下,從第一層(M1)到第三層的多層排線結構和光刻技(Lithography)。排線層和導孔電極的金屬為釕。左圖為第二層(M2)的斷面圖,右圖為M1和M3的斷面圖

一個超級導孔可以阻斷(Block)多少根(Track)M2?至少是1根。但是,imec使用的3納米代際的多層排線的尺寸如下,M1和M3為36納米Pitch,M2為21納米Pitch。用超級導孔“阻擋(Block)”Pitch最短的M2。如果僅阻擋一根的話,對M2的佈局沒有什麼影響,但很難再保持超級導孔和M2的絕緣關係。

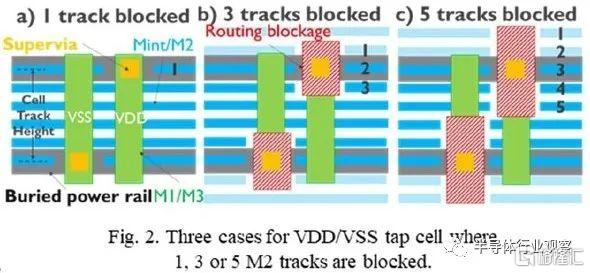

單元格(Cell)高度為5T(Track)的標磚單元(Standard Cell)中的超級導孔和第二層金屬排線(M2)的佈局。上圖為超級導孔所“Block”的M2的多條線路。左(a)為1根,中間(b)為3根,右(c)為5根

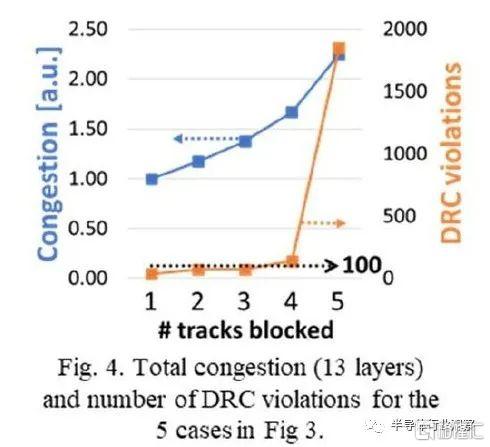

下面我們看看增加阻斷(Block)的線路後的影響。如果被阻斷(Block)的線路數量過多的話,M2的佈局就會受到阻礙。其影響如下,當佈局第三層以及網上的其他層時,會受限制,且排線會更復雜。Imec將阻斷(Block)的M2的線路數量從1根(Track)到5(Track)分別作了測試,且推斷了從第0層(Mint層)到第5層(M5)的排線複雜程度。我們把阻斷(Block)一根排線的複雜程度為看做單位“1”,阻斷3根(Track)的時候,複雜程度沒有什麼變化,4根和5根的時候,從M3到M5的複雜度急劇增加!

超級導孔所阻斷的M2的線路數量與從M0(Mint)到M5的排線複雜度的關係。當阻斷的線路數量超過3時,M3和M4、M5的排線複雜程度急劇增加。即,把阻斷(Block)一根M2排線的複雜程度為看做單位“1”

此外,如果阻斷的線路條數過多的話,佈局的設計就會很困難。多層排線的佈局設計(PnR工程)工藝中使用設計工具能夠檢測出佈局是否違反設計規定的功能(即,設計工具檢查功能,DRC)。當超級導孔阻斷的M2的線路數量增加的時候,排線的複雜度會增加,同時,違反DRC的數量也會增加。假設一款13層的排線結構,當阻斷的M2的線路達到5條時,違反DRC的數量會達到1500,甚至更多。另一方面,當被阻斷的數量小於4時,違反DRC的數量為100左右。

被阻斷的M2的線路數量和排線複雜度(左縱軸)、違反DRC數量(右縱軸)的關係。當被阻斷的線路數量為4以及以下時,違反DRC的數量為100左右。當數量為5時,違反DRC的數量會急劇增加,超過1500。以上為13層產品的推測值

接下來,我們將説明當減少單個超級導孔阻斷的排線數量時產生的問題。佈局在垂直(豎向)方向的第一層金屬排線層(M1)和第三層(M3),第二層金屬排線層(M2)為水平(橫向)方向的平行直線。並採用了Nano-sheet結構的晶體管和埋入式電源(BPR)。超級導孔直接連接M1和M3。即,超級導孔阻斷了M2。

第一層(M1)到第三層(M3)的多層排線結構、光時刻(Lithography)技術(3納米代際)。排線層和導孔電極的金屬為釕。左圖為第二層(M2)的斷面圖。右圖為M1和M3的斷面圖

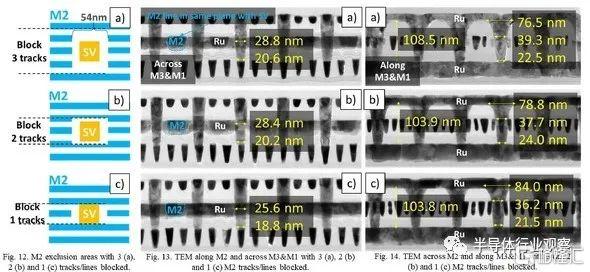

為了儘可能地提高排線佈局的自由度,需要減少阻斷的排線數量。單個超級導孔至少要阻斷一根M2排線(Track)。於是,將阻斷的排線數量從1開始逐步增加到2,3 。並以此為條件,試做了M1到M3,且測量了超級導孔的特性。

改變阻斷的排線數量後,電子顯微鏡下觀察試做的具有多層排線結構佈局圖案和斷面。左邊為阻斷的M2的排線數量。從上往下依次為3,2,1 。中間和右邊為排線結構的斷面圖,分別對應左邊的被阻斷的排線的數量。中間為與M2平行的M3和M1的斷面圖。右端為與M1和M3平行的M2的斷面圖。圖像中間的黃色數值為超級導孔的各部分的尺寸

尤其受到重視的是超級導孔和M2絕緣電阻。測量了絕緣電阻(泄露電流)後發現,當一根M2的線路被阻斷時,75%的超級導孔發生了短路不良問題。即使兩根線路被阻斷,也有10%的超級導孔發生了短路問題。當被阻斷的線路為3時,短路問題不再那麼明顯。

超級導孔和M2的絕緣電阻。縱軸為累積概率(Cumulative Probability),橫軸為電阻值

由上圖可知,至少要阻斷M2的三根線路,此外,如上文所述,當被阻斷的線路為 4或者5時,就會影響排線佈局。目前來看,三根是最理想的數量。

將阻斷了M2的三根線路的超級導孔的電阻(導孔電阻)與AR比為3的疊加導通孔(Stacked Via)的電阻比較後發現,超級導孔的導孔電阻中央值較疊加導通孔下降了1/2.4,實現了大幅度的減少。超級導孔有望成為減少導孔電阻的一項關鍵技術。

利用開爾文連接法(Kelvin )測定各種導孔的電阻值結果。阻斷M2的三根線路的超級導孔(SV)的電阻值較疊加導通孔(AR比為3)降低了1/2.4